# The Brave New Old World of Design Automation Research

Ralph K. Cavin III William H. Joyner, Jr. Walden C. Rhines Semiconductor Research Corporation Semiconductor Research Corporation Mentor Graphics Corporation

National Science Foundation Workshop on Electronic Design Automation – Past, Present, and Future July 8, 2009 Arlington, Virginia

The Brave New Old World of Design Automation Research

# "Community, Identity, Stability" – Aldous Huxley, *Brave New World*, 1932

- A community of experts from industry and universities, representing multiple disciplines

- Renewed identity as an exciting research area

- Stability of support for research and education

# The Brave New Old World of Design Automation Research

- What's old

- What happened

- What's new

- What next

# What's Old

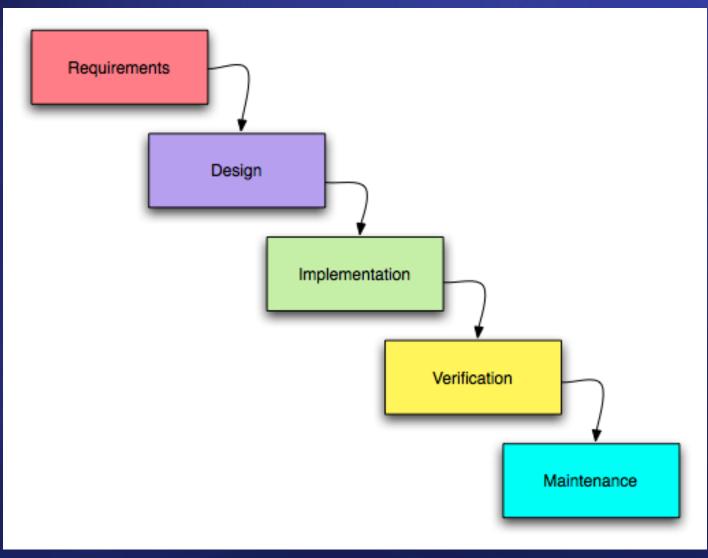

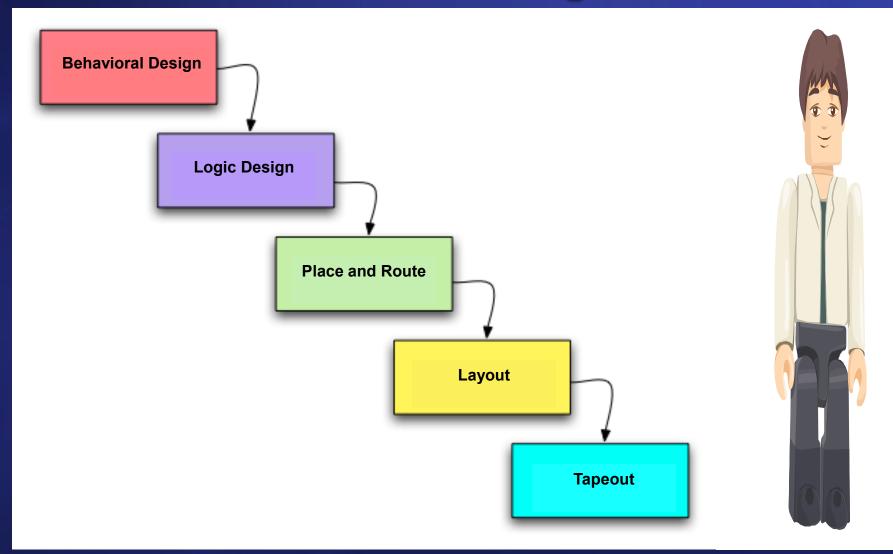

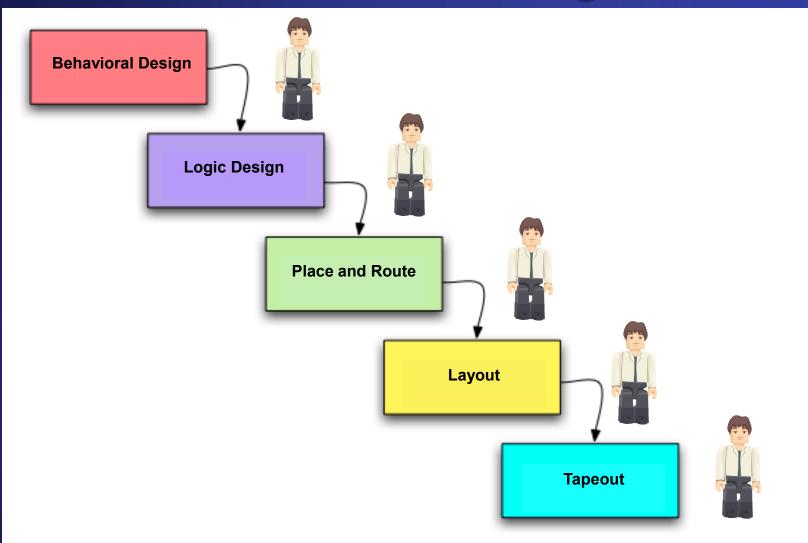

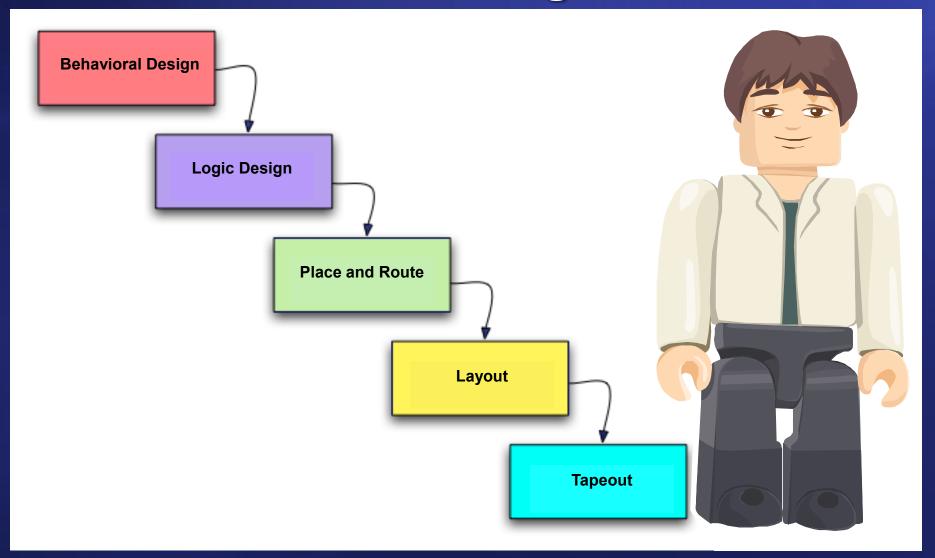

#### **Old "Waterfall" Chart**

#### Software

#### **Old "Waterfall" Chart**

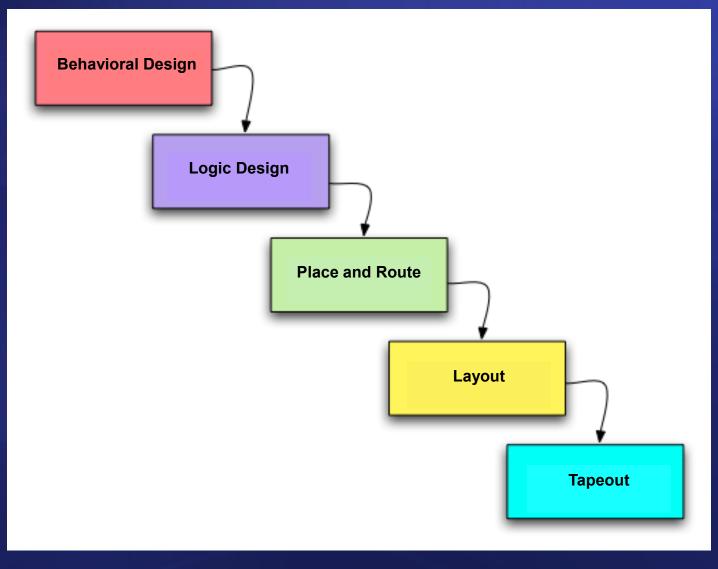

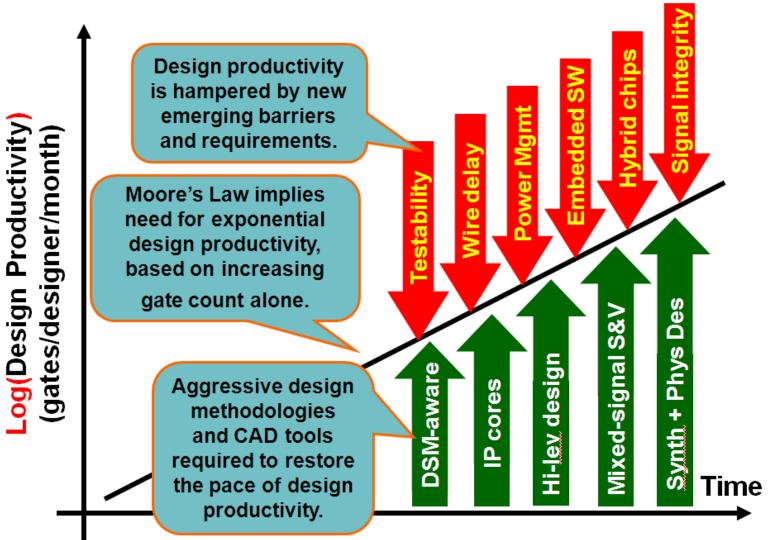

#### **Old "Productivity Gap" Chart**

# **Old "Superexponential" Chart**

#### Superexponential Design Complexity

| Thousands                                                  | Functionality + Testability                                                                                                                               |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| rnousands                                                  | Functionality + Testability + Wire Delay                                                                                                                  |  |  |  |

|                                                            | Functionality + Testability + Wire Delay + Power Mgmt                                                                                                     |  |  |  |

| # Transistors                                              | Functionality + Testability + Wire Delay + Power Mgmt<br>+ Embedded software                                                                              |  |  |  |

|                                                            | Functionality + Testability + Wire Delay + Power Mgmt + Embedded<br>software + Signal Integrity                                                           |  |  |  |

|                                                            | Functionality + Testability + Wire Delay + Power Mgmt + Embedded<br>software + Signal Integrity + Hybrid Chips                                            |  |  |  |

| Billions                                                   | Functionality + Testability + Wire Delay + Power Mgmt + Embedded software<br>+ Signal Integrity + Hybrid Chips + RF                                       |  |  |  |

|                                                            | Functionality + Testability + Wire Delay + Power Mgmt + Embedded software +<br>Signal Integrity + Hybrid Chips + RF + Packaging                           |  |  |  |

|                                                            | Functionality + Testability + Wire Delay + Power Mgmt + Embedded software + Signal<br>Integrity + Hybrid Chips + RF + Packaging + Mgmt of Physical Limits |  |  |  |

| Exponentially growing number of elements (devices & wires) |                                                                                                                                                           |  |  |  |

| Design complexity is exponential function of element count |                                                                                                                                                           |  |  |  |

## **Old "Wilting Rod" Chart**

#### **Difficulty of Sustaining Design Productivity**

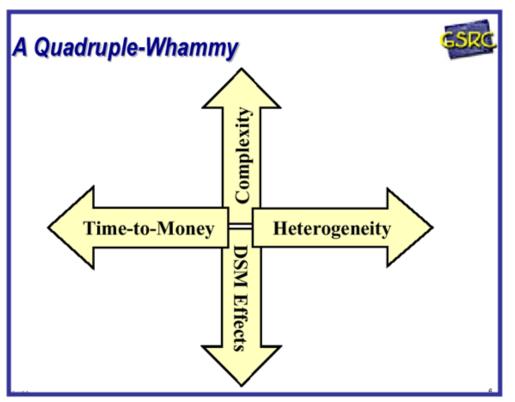

# **Old "Quadruple Whammy" Chart**

#### "Quadruple Whammy" for Design and Tools

- Design of each transistor and wires harder

- Exponentially more transistors

- More elements doing different things

- Greater design risk, greater variety, and smaller design window

Source: Kurt Keutzer 20<sup>th</sup> century

# **Tall Thin Designers**

| CARVER MEAD · LYNN CONWAY                        |  |  |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|--|--|

|                                                  |  |  |  |  |  |  |  |

| CALLER ALLER THE SHORE AND THE SHORE AND A SHORE |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

|                                                  |  |  |  |  |  |  |  |

#### **Tall Thin Designers**

#### **Short Thin Designers**

#### **Tall Fat Designers**

#### **Foundations of Computer Science**

#### FOCS 2008 1/78 in circuit and logic design/minimization

#### FOCS 1960, 1961 30/33 in circuit and logic design/minimization Muroga, Akers, Roth, McCluskey, Karp, ...

#### **FOCS 2009**

50th Annual IEEE Symposium on Foundations of Computer Science

> October 24-27, 2009 Atlanta, GA

# Examples of the research articles in semiconductors that resulted in Nobel Prizes

|                                                                                                                    | Nobel Prize |                                             | # of citations                  |                 |

|--------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------|---------------------------------|-----------------|

| Article                                                                                                            | in:         | for:                                        | 25 years<br>from<br>publication | through<br>2008 |

| Bardeen J, Brattain WH "The<br>Transistor, a Semi-conductor<br>Triode", Phys. Rev. 74 (2): 230-231<br>1948         | 1956        | Discovery of<br>semiconductor<br>transistor | 71                              | 235             |

| Esaki L, "New Phenomenon in<br>Narrow Germanium p-n Junctions",<br>Phys. Rev. 109 (1958) 603                       | 1973        | Discovery of tunnel diode                   | 247                             | 547             |

| Kroemer H, "Heterostructure<br>Bipolar-transistors and Integrated-<br>circuits", Proc. of the IEEE 70<br>(1982) 13 | 2000        | Invention of heterojunctions                | 577                             | 609             |

#### Source: Victor Zhirnov, SRC

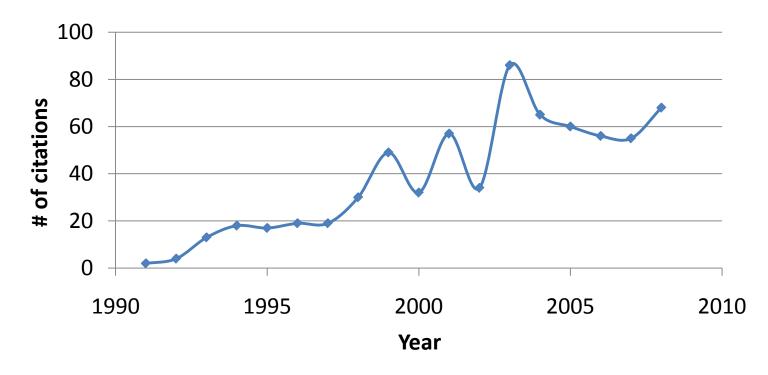

# **Publication Lifetime**\*

Example: Design/CADTS

"Asymptotic Waveform Evaluation for Timing Analysis", by Pileggi and Rohrer, IEEE Trans. Computer-Aided Design 9 (4)352 (1990)

677 citations

188 citations by industry (28%)

\*Average lifetime is 5 years

Source: Victor Zhirnov, SRC

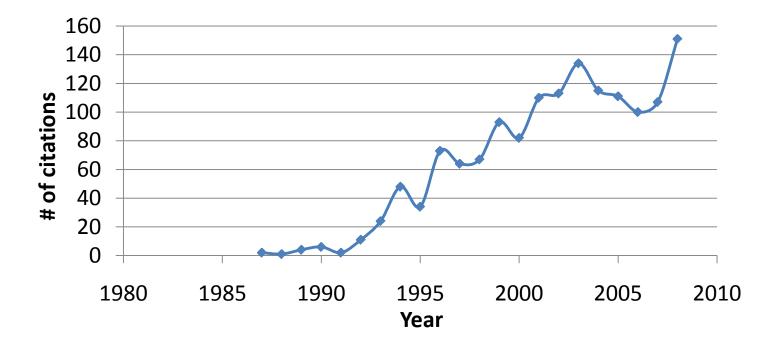

# **Publication Lifetime**\*

Example: Design/CADTS

"Graph-based Algorithms for Boolean Function Manipulation" by R. E. Bryant, IEEE Trans. Computers 35 (8): 677 (1986)

1443 citations

283 citations by industry (25%)

\*Average lifetime is 5 years

Source: Victor Zhirnov, SRC

#### What Happened

NSF 2006 Forum on Future Directions in Design Automation Research

- Held October 30-31, 2006, at NSF in Arlington, Virginia

- Leading researchers and engineers assembled:

- 12 faculty from leading universities

- 11 industry researchers

- 8 NSF participants

- Panels, presentations helped develop findings

Source: 2006 Forum <sup>20</sup>

#### Attendees

- Arvind

- Tim Cheng

- Jason Cong

- Hugo DeMan

- John Hayes

- Mark Horowitz

- Sharad Malik

- Steve Nash

- Rob Rutenbar

- Sachin Sapatnekar

- Ken Shepard

- Jacob White

- Ralph Cavin

SRC

- Steve Hillenius

- William Joyner

- Jeff Welser

MIT UCSB UCLA Leuven Michigan Stanford Princeton GMU CMU Minnesota Columbia MIT

SRC

SRC

SRC

Luigi Capodieci AMD Ameesh Desai LSI Logic Andreas Kuehlmann Cadence IBM David Kung Jeff Parkhurst Intel Juan Rey Mentor David Yeh ΤI Sankar Basu NSF NSF Tony Chan Mike Foster NSF Peter Freeman NSF Larry Goldberg NSF Peter March NSF NSF Usha Varshney

Source: 2006 Forum <sup>21</sup>

#### Three Grand Challenges in Design Automation

Challenges in design automation are many, but they can be grouped into three areas:

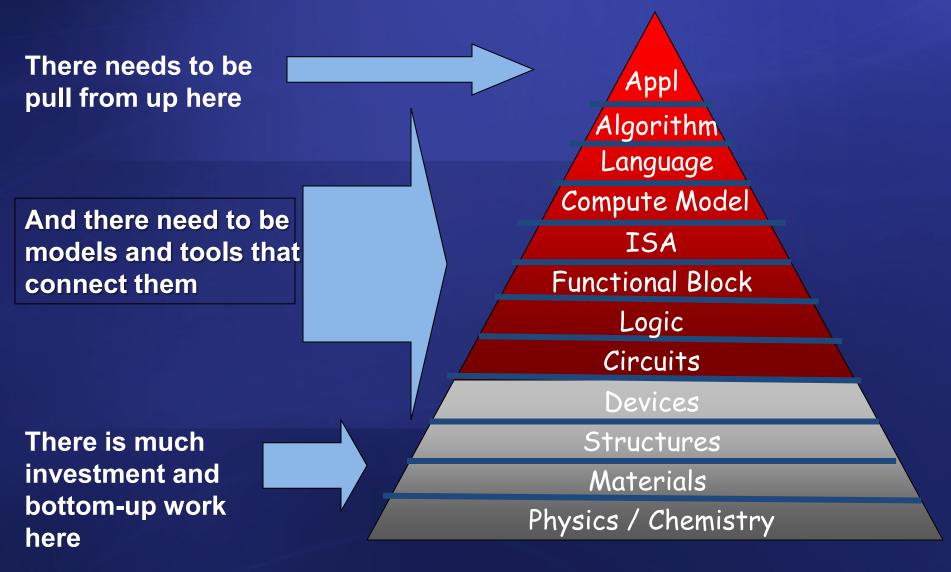

- System-level design is needed at the top to increase the productivity of designers – otherwise efficient use cannot be made of advanced devices and materials

- Robust optimization in the middle is necessary to contain the exploding complexity of systems and to offset the diminishing returns afforded by feature size shrinkage

- Design for manufacturing at the back end (and throughout the flow) is critical to assure that we can produce products using new technologies

Models and abstractions are key at all levels of the design process Source: 2006 Forum <sup>22</sup>

- System level techniques are needed to achieve shorter design times with higher quality to address system level problems: clock, power management, interconnection, fault tolerance, ...

- Design tools must extend to where design is going, including the software level

- A compositional method of designing and connecting modules such that the functionality and performance are predictable is needed; it must be aware of implementability, verification, test, and reliability

- A design flow and methodology must enable more sophisticated handoffs; a collaborative framework must focus on the interfaces between abstraction levels to allow stable robust, reusable design IP

- We must be able to implement hybrid systems efficiently model, explore, design, optimize, and integrate non-digital functionality (MEMS, NEMS, analog/RF, sensors/transducers, photonics, biological, ...)

Source: 2006 Forum <sup>23</sup>

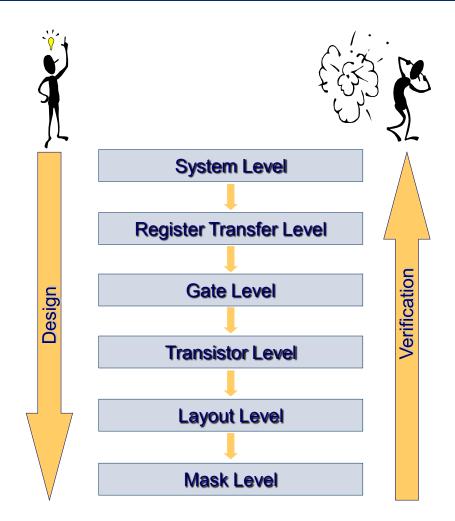

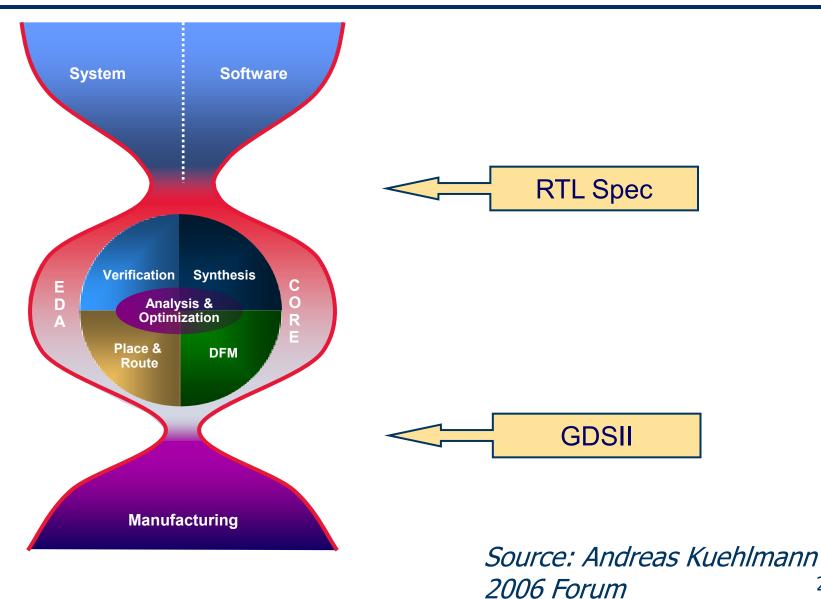

Ever Increasing Design Flow Complexity

- Expansion of traditional RTL-to-layout DA support

- Upwards: System specification, transaction level modeling, behavioral synthesis

- Downwards: RET, OPC, yield optimization through postlayout manipulations, etc.

- In between: more and more complex optimizations

*Source: Andreas Kuehlmann* 2006 Forum <sup>24</sup>

#### Most of Design Automation Today Focuses on the "Middle"

25

- Optimization algorithms must be what many of today's design automation techniques are not: stable, scaleable, and robust

- Design automation must leverage optimization technology casting problems in optimization terms opens a new resource of partnerships in cross-disciplinary research that can lead to better optimization engines

- Optimization algorithms need to handle multiple objectives simultaneously to address critical power, variability, manufacturability,

- Techniques must globally optimize performance across layers of abstraction and diverse technologies

#### Source: 2006 Forum <sup>26</sup>

# Se Technology/Manufacturing Challenges

- Design for manufacturing must move from handling variability to robust operation in the face of failures from multiple sources

- Design tools must comprehend multiple options associated with new devices, new materials, fabrics and 3D stacking

- Communication between layout/design must go beyond sets of rules to process/manufacturing understanding at all levels.

- Tools must comprehend hybrid devices and materials as well as emerging nontraditional applications (bio, sensor, medical, etc.)

- Design techniques addressing these late-CMOS technology challenges must bridge to beyond-CMOS nanotechnologies as well

Source: 2006 Forum <sup>27</sup>

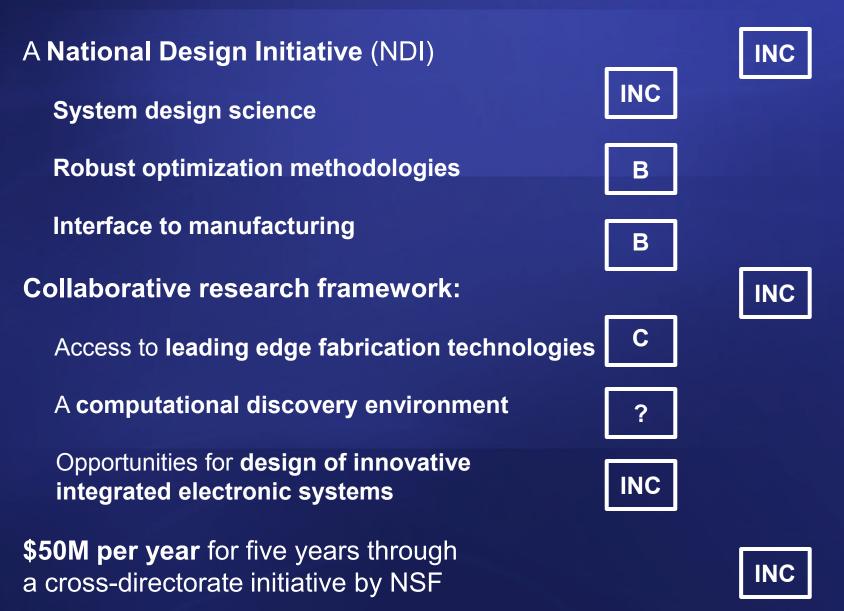

- Since design automation is critical to advancing our computing capability for the 21<sup>st</sup> century:

- NSF should support a collaborative platform for design automation research pushing towards beyond-CMOS technologies

- NSF must establish and support multidisciplinary partnerships to enable the design technology work necessary for 21<sup>st</sup> century leadership:

- enabling system-level design in partnership with the software and architecture areas

- ✓ with larger-scale, more robust **optimization** to provide more complex systems and keep on Moore's Law pace

- ✓ at the **nanoscale** to take design technology from novel devices to system-level applications

Source: 2006 Forum <sup>28</sup>

- Design will be a key differentiator for US competitiveness and national security.

- US must have the most productive designers

- Design costs dominate they need to be dramatically reduced in terms of team size, design time, etc. to maintain US lead

- National support for design research is diminishing in US, increasing elsewhere.

- China, Europe, Taiwan, and Canada all support university-based design research infrastructure

- National strategy in design needs to match national investment in materials and technologies

- Education funding must help supply trained scientists and engineers

- Moore's Law is a critical enabler for advances in computing and its future depends on design

- Materials and process technology alone cannot keep us on the Moore's Law curve.

- Advanced applications DNA sequencing, astrophysics, cryptography rest on this computational foundation

Source: 2006 Forum <sup>29</sup>

## The 2006 Forum – A Report Card

## What's New

#### What's New (Well, Not Really New)

- New emphasis on parallelism

- New ITRS design and software emphasis

- New focus on applications

- New post-CMOS technologies

- New (old) predictions about the death of EDA

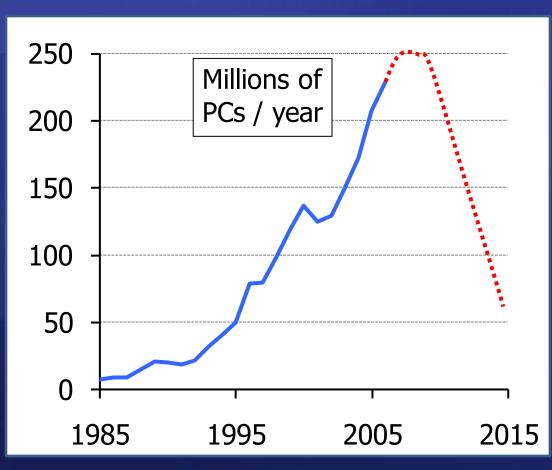

# **The Sequential Peril**

#### Cores not faster + no parallel improvement → SW not faster → no new PC sales except for wearout → sales drop 250M ↓ 50M

Source: Dave Patterson, SRC, 2004

# SRC/NSF Joint Program on Multicore Design and Architecture

- Joint needs development, solicitation, and selection of projects in multi-core architecture, design, tools, and interconnect

- \$10M, 3-year program

- 28 new tasks from 27 universities with 43 faculty (including 17 new investigators and 7 former SRC students) selected for 8/09 starts

## New Emphases in 2008 ITRS

- Importance of software as an integral part of semiconductor products

- Software design productivity as a key driver of overall design productivity

- Heavy use of special purpose multi-core architectures as a key enabler of productivity growth

- Continued emphasis on system-level design

- Special section on energy

- New term *Design Equivalent Scaling* refers to design technologies that enable high performance, low power, high reliability, low cost, and high design productivity.

International Technology Roadmap for Semiconductors

# Compelling Laptop/Handheld Apps

#### Health Coach

- Since laptop/handheld always with you, Record images of all meals, weigh plate before and after, analyze calories consumed so far

- "What if I order a pizza for my next meal? A salad?"

- Since laptop/handheld always with you, record amount of exercise so far, show how body would look if maintain this exercise and diet pattern next 3 months

- "What would I look like if I regularly run 2 miles? 4 miles?"

#### Face Recognizer/Name Whisperer

Laptop/handheld scans faces, matches image database, whispers name in ear (relies on Content Based Image Retreival)

Source: Dave Patterson, SRC, 2004

Source: Rob Rutenbar

#### **Ultimate Measures of Success ...**

For the *technologist*: I/V curve in *Nature*  For the *circuit designer*: Best Paper Award at ISSCC

SNB CWG4 Report

(Rob Rutenbar, 2004)

#### Algorithms, Coding, Logic, Architectures, Applications

Key question: Will the behavior of nanodevices be so strange that our "higher level" abstractions need to change?

Key answers:

NO, a switch is a switch

**YES**, that's the whole idea

# NRI 2009 Architecture Benchmarking Exercise

Magnetic Tunnel Junction **Spin Wave Devices** Mag Dot Logic BiSFET **Graphene Veselago Devices** Excitons **Magnetic Rings Tunnel FETs** Nanomagnet logic **Plasmonic logic** Graphene thermal logic Graphene spin transport **Binary Decision Diagram Arch** Multiferroic based devices

UCLA Markovic UCLA Khitun Roychowdhury UCLA Register UT SUNY Lee MIT Baldo MIT Ross ND Seabaugh Niemier ND Michigan Mazumder Chen Purdue Purdue Ye PSU Datta Salahuddin UCB

WIN WIN WIN SWAN INDEX **INDEX** INDEX MIND MIND MIND MIND MIND MIND WIN

# **EDA Myths and Realities in 2009**

- EDA is rewith rippontualities ploase from solving new problems

- Adoption of heading-bodgle systemisis bonding tor technology is the same rate as in the past

- Overe ian de Dérovatilkent at a btiszeschinierel is i accomposition in arket share changes

- EDApasies denteessing betgessingerasterse Aniconductor manufacturing cost

- Companies acensiooticeationgay or a ordinberstownactasis glassing and a bflowsplatforms

- Semiconductor industry has a somstolide ting posolidating

Source: Wally Rhines, DesignCon 2009

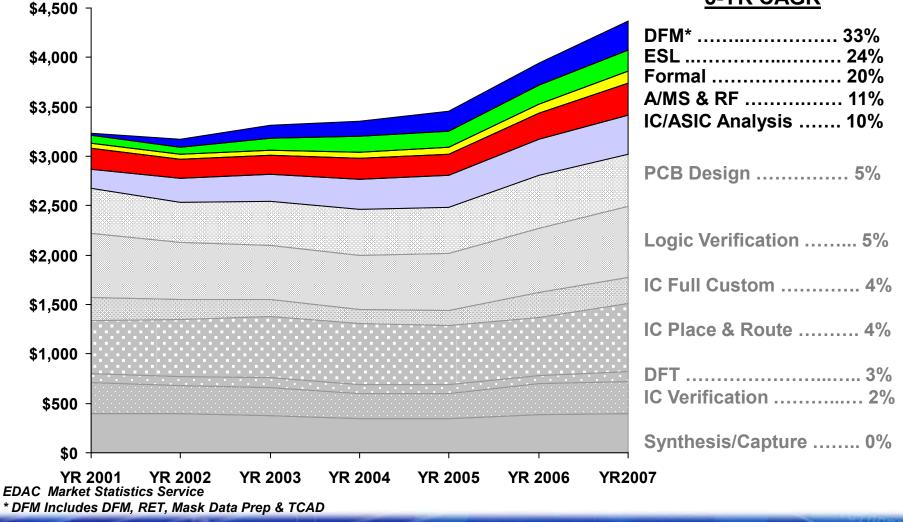

#### New Methodologies Drive EDA Revenue Growth 5-YR CAGR

# Graphics

Source: Wally Rhines, DesignCon 2009

#### What Next

National Science Foundation Workshop on Electronic Design Automation – Past, Present, and Future July 8-9, 2009

#### What Next – This Workshop

- A community of experts from industry and universities, representing multiple disciplines

- Renewed identity as an exciting research area

- Stability of support for research and education

#### **The Food Pyramid**

Source: Rob Rutenbar

#### What Next – This Workshop

- Strengthen the links between theory of computation and design automation

- Maintain strong industry/university/government partnerships

- Grow support for design and design automation as increasingly important contributors to the roadmap forward