## EDA Challenges in Systems Integration

J. A. G. Jess NSF EDA Workshop July 8 and 9, 2009

# Why should IC-EDA and Electronics Systems Manufacturers move closer?

- With Moore's Law electronic systems move to become IC's – off-chip communication moves on-chip facing IC designers with systems communication legacy

- Electronics Systems market is roughly six times the market of IC's – interesting for EDA to have the ESM's as customers

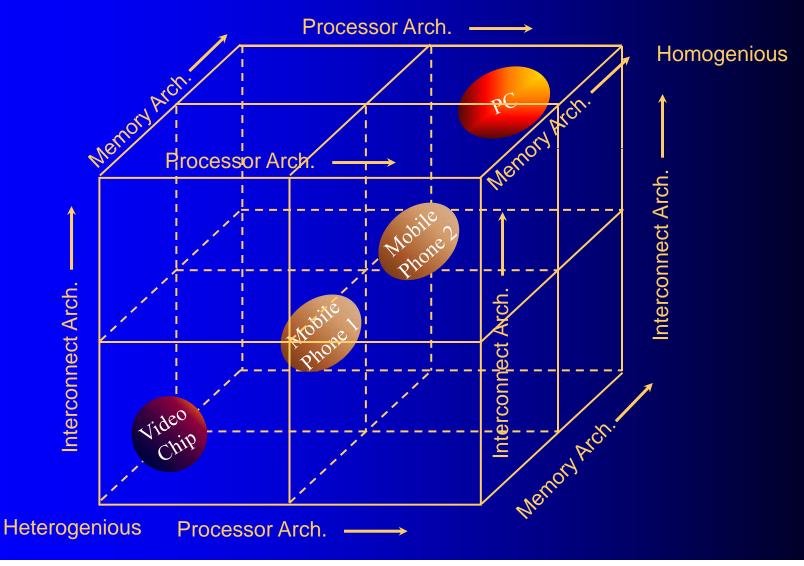

# Two Paradigms: Heterogeneous - Homogeneous

heterogeneous

homogeneous

| Many specialized (optimized)<br>compute engine types                    | Computing          | A few (at times frequently<br>replicated) general compute<br>engine types (X86 API,) |

|-------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------|

| Many specialized<br>"communication fabrics"                             | Communi-<br>cation | A few universally used<br>standard bus protocols<br>(PCIe, AMBA AXI,)                |

| Many different memory<br>types, designer in control<br>of memory policy | Memory             | Standard (virtual)<br>Random Access Memory<br>supported by caches                    |

## Attempt of a Taxonomy

| Heterogeneous                                                                                                                      | Homogeneous                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Good Compute Performance<br/>to Power Ratio (MOPs/Wsec)</li> <li>Small "Bill of Material"<br/>(BoM, e.g. area)</li> </ul> | <ul> <li>Compute Performance to</li> <li>Power Ratio medium</li> <li>(improving!) but unpredictable</li> <li>BoM medium to large</li> </ul> |

| <ul> <li>Lack of Flexibility</li> <li>Large NRE cost, limited reuse</li> </ul>                                                     | <ul> <li>Very flexible through programming on "Virtual Machine"</li> <li>Extensive re-use of SW and HW</li> </ul>                           |

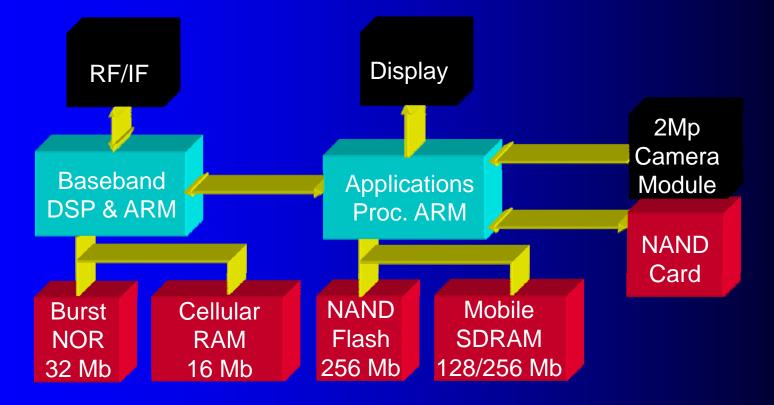

# Sample Hardware Architecture Mobile Device (~2005)

### **Devices sharing Interconnect**

### Heterogenity vs. Homogenity

#### **Basic Challenges**

- How to assign performance metrics to the co-ordinates of the cube?

- Given those metrics, how to establish tools providing decision support for designers (and roadmap makers)?

#### "Systems Integration"

- A large portion of the design effort is concerned with matching the on-chip and inter-chip communication- and memory performance with the specifications

- Communication is critical for Timing and Power

- How deal with contention on shared interconnect?

- Stability of system modes and mode-transitions?

- Verification is hampered by the lack of formal design documentation on system level

- Up to now there seems to be little tooling support – lots of manual code development & guessing

Thank you!